## **ANALOG DEVICES**

## True Differential,Dual,1 MSPS, 14-Bit/12-Bit, 2-Channel SAR ADC With PGA

### **Preliminary Technical Data**

# AD7264/AD7262

### FEATURES

Dual Simultaneous sampling 14-bit/12-bit, 2-channel ADC **True Differential Analog Inputs Programmable Gain Stage:** ×1, ×2, ×3, ×4, ×6, ×8, ×12, ×16, ×24, ×32, ×48, ×64, ×96, x128 AD7264 Throughput rate per ADC: 1 MSPS AD7262 Throughput rate per ADC: 1 MSPS Analog Input impedance: >  $1G\Omega$ Wide input bandwidth -3dB bandwidth: > 100 kHz 4 On-chip Comparators Specified for  $V_{cc}$  of 5 V ± 5% Low current consumption: 24mA **Guaranteed Monotonic Device offset calibration** System offset and gain calibration On-chip reference: 2.5 V -40°C to +105°C operation High speed serial interface SPI®/QSPI™/MICROWIRE™/DSP compatible 48-lead TQFP/LFCSP Package

### **GENERAL DESCRIPTION**

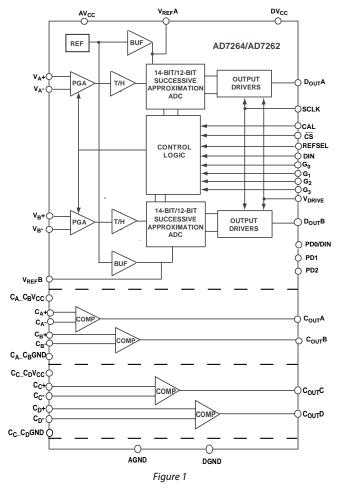

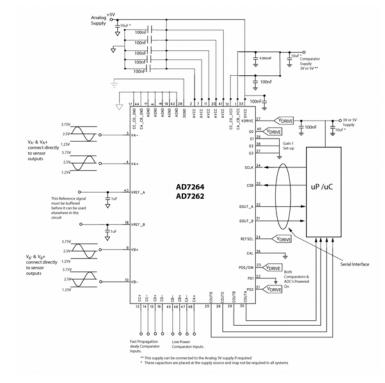

The AD7264/AD7262 are dual, 14-bit/12-bit, high speed, low power, successive approximation ADC that operates from a single 5 V power supply and features throughput rates up to 1MSPS, per on-chip ADC. Two Complete ADC Functions Allow Simultaneous Sampling and Conversion of Two Channels. The conversion result of both channels is simultaneously available on separate data lines, or in succession on one data line if only one serial port is available. The device contains two ADCs, each preceded by a true differential analog input with a PGA. There are thirteen gain settings available,  $\times 1$ , ×2, ×3, ×4, ×6, ×8, ×12, ×16, ×24, ×32, ×48, ×64, ×96 and x128. In addition, the AD7264/AD7262 contains four comparators. Comparators A and B are optimised for low power while comparator C and D have short propagation delays. The AD7264/AD7262 features a calibration function to remove the devices offset error and programmable offset and gain adjust registers to allow for input path (e.g. sensor) offset and gain compensation. The AD7264/AD7262 has an on-chip 2.5 V reference that can be overdriven if an external reference is preferred. The AD7264/AD7262 is available in a 48-lead TQFP or LFCSP package.

#### Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### FUNCTIONAL BLOCK DIAGRAM

#### **Table 1.Related Products**

| Device<br>Number | Resolution | Throughput<br>Rate | Number of<br>Channels |

|------------------|------------|--------------------|-----------------------|

| AD7264           | 14-Bit     | 1 MSPS             | Dual, 2-ch            |

| AD7262           | 12-Bit     | 1 MSPS             | Dual, 2-ch            |

| AD7264-5         | 14-Bit     | 500 KSPS           | Dual, 2-ch            |

| AD7262-5         | 12-Bit     | 500 KSPS           | Dual, 2-ch            |

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

### TABLE OF CONTENTS

| FEATURES 1                                   |

|----------------------------------------------|

| GENERAL DESCRIPTION 1                        |

| FUNCTIONAL BLOCK DIAGRAM 1                   |

| Revision History                             |

| Specifications For AD7264                    |

| Specifications For AD72625                   |

| Timing Specifications7                       |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions9 |

| Terminology11                                |

| Modes of Operation                           |

## **Preliminary Technical Data**

| Pin Driven Mode14      |  |

|------------------------|--|

| Gain Selection         |  |

| Power Down Modes       |  |

| Calibration            |  |

| Control Register       |  |

| Theory of operation    |  |

| Circuit Information 12 |  |

| V <sub>DRIVE</sub>     |  |

| Reference              |  |

| Serial interface       |  |

| Outline Dimensions     |  |

| Ordering Guide         |  |

### **REVISION HISTORY**

09/06—Revision PrE: Initial Version

### **SPECIFICATIONS FOR AD7264**

$AV_{CC} = DV_{CC} = 5 V \pm 5\%$ ,  $C_A\_C_BV_{CC} = C_C\_C_DV_{CC} = 2.7 V$  to 5.25V,  $V_{DRIVE} = 2.7 V$  to 5.25V,  $f_{SAMPLE} = 1$  MSPS,  $f_{SCLK} = 34$ MHz,  $V_{REF} = 2.5 V$  Internal/External;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted<sup>1</sup>.

#### Table 2.

| Parameter                                                           | Value                                           |       |                                                 | Unit              | Test Conditions / Comments                           |

|---------------------------------------------------------------------|-------------------------------------------------|-------|-------------------------------------------------|-------------------|------------------------------------------------------|

|                                                                     | Min                                             | Тур   | Max                                             | -                 |                                                      |

| DYNAMIC PERFORMANCE                                                 |                                                 |       |                                                 |                   | $f_{IN} = 100 \text{ kHz}$ sine wave;                |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>                            | 78                                              | 80    |                                                 | dB                | PGA Gain setting = 1                                 |

| Signal-to-Noise + Distortion Ratio (SINAD) <sup>2</sup>             | 77                                              |       |                                                 | dB                |                                                      |

| Total Harmonic Distortion (THD) <sup>2</sup>                        |                                                 | -82   |                                                 | dB                |                                                      |

| Spurious Free Dynamic Range (SFDR) <sup>2</sup>                     |                                                 | -82   |                                                 | dB                |                                                      |

| Common Mode Rejection Ratio (CMRR) <sup>2</sup>                     |                                                 | <-70  |                                                 | dB                | For ripple frequency of 50/60Hz; see Figure x.       |

| Channel-to-Channel Isolation <sup>2</sup>                           |                                                 | -88   |                                                 | dB                |                                                      |

| Bandwidth                                                           |                                                 | 100   |                                                 | kHz               | @ -3 dB; PGA gain setting = 128                      |

| DC ACCURACY                                                         |                                                 |       |                                                 |                   |                                                      |

| Resolution                                                          |                                                 |       | 14                                              | Bits              |                                                      |

| Integral Nonlinearity <sup>2</sup>                                  |                                                 |       | ±2                                              | LSB               |                                                      |

| Differential Nonlinearity <sup>2</sup>                              |                                                 |       | ±0.99                                           | LSB               | Guaranteed no missed codes to 14 bits                |

| Offset Error <sup>2</sup>                                           |                                                 |       | ±5                                              | LSB               | After Calibration                                    |

| Offset Error Match <sup>2</sup>                                     |                                                 | ±1    |                                                 | LSB               |                                                      |

| Offset Drift                                                        |                                                 | 5     |                                                 | μV/°C             |                                                      |

| Gain Error <sup>2</sup>                                             |                                                 | ±0.1% | TBD                                             | FSR               |                                                      |

| Gain Error Match                                                    |                                                 | ±0.5  |                                                 | LSB               |                                                      |

| ANALOG INPUT                                                        |                                                 |       |                                                 |                   |                                                      |

| Input Voltage Range: V <sub>+</sub> and V <sub>-</sub> <sup>3</sup> | V <sub>CM</sub> -<br>V <sub>REF</sub> /(2xGain) |       | V <sub>CM</sub> +<br>V <sub>REF</sub> /(2xGain) | v                 | For Gain >1, $V_{CM} = AV_{CC}/2$                    |

| Common mode Voltage, V <sub>CM</sub>                                | 2.5V- 100mV                                     |       | 2.5V +100mV                                     | V                 | F                                                    |

| DC Leakage Current                                                  |                                                 |       | ±1                                              | μΑ                |                                                      |

| Input Capacitance                                                   |                                                 | 3     |                                                 | pF                |                                                      |

| Input Impedance                                                     |                                                 | >1    |                                                 | GΩ                |                                                      |

| REFERENCE INPUT/OUTPUT                                              |                                                 |       |                                                 |                   |                                                      |

| Reference Output Voltage <sup>4</sup>                               | +2.49                                           |       | +2.51                                           | v                 | ±0.2% max @ 25°C                                     |

| Reference Input Voltage Range                                       | +2.49                                           |       | +2.51                                           | V                 |                                                      |

| DC Leakage Current                                                  |                                                 |       | ±1                                              | μA                | External reference applied to Pin<br>VREFA/Pin VREFB |

| Input Capacitance                                                   |                                                 | 25    |                                                 | pF                |                                                      |

| V <sub>REF</sub> A, V <sub>REF</sub> B Output Impedance             |                                                 | 10    |                                                 | Ω                 |                                                      |

| Reference Temperature Coefficient                                   |                                                 | 20    |                                                 | ppm/°C            |                                                      |

| V <sub>REF</sub> Noise                                              |                                                 | 20    |                                                 | μV <sub>RMS</sub> |                                                      |

| LOGIC INPUTS                                                        | 1                                               | -     |                                                 | L. mile           |                                                      |

| Input High Voltage, VINH                                            |                                                 |       |                                                 | v                 |                                                      |

| Input Low Voltage, Vinc                                             | Dive                                            |       | 0.8                                             | v                 |                                                      |

| Input Current, In                                                   |                                                 |       | ±1                                              | μA                |                                                      |

| Input Capacitance, $C_{\mathbb{N}}^4$                               |                                                 | 5     |                                                 | pF                |                                                      |

|                                                                     |                                                 |       |                                                 |                   |                                                      |

**Preliminary Technical Data**

|                                                | 1                        |          |      |           |                                                                                                                    |

|------------------------------------------------|--------------------------|----------|------|-----------|--------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS                                  |                          |          |      |           |                                                                                                                    |

| Output High Voltage, V <sub>OH</sub>           | V <sub>DRIVE</sub> - 0.2 |          |      | V         |                                                                                                                    |

| Output Low Voltage, V <sub>OL</sub>            |                          |          | 0.4  | V         |                                                                                                                    |

| Floating State Leakage Current                 |                          |          | ±1   | μΑ        |                                                                                                                    |

| Floating State Output Capacitance <sup>4</sup> |                          | 10       |      | pF        |                                                                                                                    |

| Output Coding                                  |                          |          |      | Two's Con | nplement                                                                                                           |

| CONVERSION RATE                                |                          |          |      |           |                                                                                                                    |

| Conversion Time                                |                          |          | 530  | ns        | $18 \times t_{SCLK}$ , For 4.75V <v<sub>DRIVE <math>\leq</math> 5.25V</v<sub>                                      |

| Cycle Time                                     |                          |          | 970  | ns        | $33 \times t_{\text{SCLK}}$ , For 4.75V $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| AC Acquisition Time <sup>4</sup>               |                          |          | 440  | ns        | For 4.75V <v<sub>DRIVE≤5.25V</v<sub>                                                                               |

| Throughput Rate                                |                          |          | 1    | MSPS      | For 4.75V <v<sub>DRIVE≤5.25V</v<sub>                                                                               |

|                                                |                          | >750     | TBD  | KSPS      | For 2.7V≤V <sub>DRIVE</sub> ≤4.75V                                                                                 |

| COMPARATORS                                    |                          |          |      |           |                                                                                                                    |

| Input Offset range                             |                          |          | ±4.5 | mV        |                                                                                                                    |

|                                                |                          | ±2.5     |      | mV        |                                                                                                                    |

| Input Common Mode Range                        |                          | 0 to 3.5 |      | v         |                                                                                                                    |

| Input Impedance                                |                          | >1       |      | GΩ        |                                                                                                                    |

| I <sub>DD</sub> Normal Mode (Static)           |                          |          |      |           | No Load, C <sub>OUT</sub> =0V                                                                                      |

| Comparator A & B                               |                          | 0.90     |      | μA        | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                          |

| <i>un</i>                                      |                          | 1.80     |      | μΑ        | $C_{A}C_{B}V_{CC} = 5V$                                                                                            |

| Comparator C & D                               |                          | 13       |      | μΑ        | $C_{c}C_{D}V_{cc} = 2.7V$                                                                                          |

|                                                |                          | 27.0     |      | μΑ        | $C_{C}C_{D}V_{CC} = 5V$                                                                                            |

| Propagation Delay Time- High to Low            |                          | 27.0     |      | μπ        |                                                                                                                    |

| Comparator A & B                               |                          | 2.30     |      | μs        | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                          |

|                                                |                          | 1.70     |      | μs        | $C_{A}C_{B}V_{CC} = 5V$                                                                                            |

| Comparator C & D                               |                          | 0.20     |      |           | $C_{A} = C_{B} V_{CC} = 3V$<br>$C_{C} = 2.7V$                                                                      |

|                                                |                          | 0.20     |      | μs        | $C_{c}C_{D}V_{cc} = 2.7V$<br>$C_{c}C_{D}V_{cc} = 5V$                                                               |

| Propagation Delay Time- Low to High            |                          | 0.14     |      | μs        | $C_{C}C_{D}VC = 5V$                                                                                                |

| Comparator A & B                               |                          | 1.70     |      |           | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                          |

|                                                |                          |          |      | μs        |                                                                                                                    |

|                                                |                          | 0.90     |      | μs        | $C_{A}C_{B}V_{CC} = 5V$                                                                                            |

| Comparator C & D                               |                          | 0.210    |      | μs        | $C_{C}C_{D}V_{CC} = 2.7V$                                                                                          |

|                                                |                          | 0.12     |      | μs        | $C_{C}C_{D}V_{CC} = 5V$                                                                                            |

| POWER REQUIREMENTS                             |                          |          |      |           | Digital I/Ps = $0 V \text{ or } V_{DRIVE}$                                                                         |

| AV <sub>DD</sub>                               | 4.75                     |          | 5.25 | V         |                                                                                                                    |

| DV <sub>DD</sub>                               | 4.75                     |          | 5.25 | V         | Throughput Rate = 1Msps                                                                                            |

|                                                | 2.7                      |          | 4.75 | V         | Throughput Rate < 1Msps⁵                                                                                           |

| $C_{A}C_{B}V_{CC}, C_{C}C_{D}V_{CC}$           | 2.7                      |          | 5.25 | V         |                                                                                                                    |

| V <sub>DRIVE</sub>                             | 2.7                      |          | 5.25 | V         |                                                                                                                    |

| I <sub>DD</sub>                                |                          |          |      |           |                                                                                                                    |

| Normal Mode (Static)                           |                          |          | 19   | mA        | $V_{DD} = 5.25 V$                                                                                                  |

| Operational                                    |                          |          | 24   | mA        | $f_s = 1MSPS$ , $V_{DD} = 5.25 V$                                                                                  |

| Shut-Down Mode                                 |                          |          | 1    | μΑ        |                                                                                                                    |

| Power Dissipation                              |                          |          |      |           |                                                                                                                    |

| Normal Mode (Operational)                      |                          |          | 120  | mW        |                                                                                                                    |

| Shut-Down                                      |                          |          | 5.25 | μW        |                                                                                                                    |

$^1$  Temperature range is  $-40^\circ$ C to  $+105^\circ$ C  $^2$  See Terminology section.  $^3$  For Gain =1 the maximum analog input signal is V<sub>CM</sub>±1.0V

<sup>4</sup> Refers to pins V<sub>REF</sub>A or V<sub>REF</sub>B.

<sup>5</sup> The AD7262 is functional but the performance specified in this specification table does not applies with these conditions.

### **SPECIFICATIONS FOR AD7262**

$AV_{CC} = DV_{CC} = 5 V \pm 5\%$ ,  $C_A\_C_BV_{CC} = C_C\_C_DV_{CC} = 2.7 V$  to 5.25V,  $V_{DRIVE} = 2.7 V$  to 5.25V,  $f_{SAMPLE} = 1$  MSPS,  $f_{SCLK} = 32$ MHz,  $V_{REF} = 2.5 V$  Internal/External;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted<sup>1</sup>.

#### Table 3.

| Parameter                                                           | Value                                           |       |                                                     | Unit              | Test Conditions / Comments                                                     |

|---------------------------------------------------------------------|-------------------------------------------------|-------|-----------------------------------------------------|-------------------|--------------------------------------------------------------------------------|

|                                                                     | Min                                             | Тур   | Max                                                 | -                 |                                                                                |

| DYNAMIC PERFORMANCE                                                 |                                                 |       | -                                                   |                   | $f_{IN} = 100 \text{ kHz}$ sine wave;                                          |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>                            | 69                                              | 72    |                                                     | dB                | PGA Gain setting = 1                                                           |

| Signal-to-Noise + Distortion Ratio (SINAD) <sup>2</sup>             | 69                                              |       |                                                     | dB                |                                                                                |

| Total Harmonic Distortion (THD) <sup>2</sup>                        |                                                 | -80   |                                                     | dB                |                                                                                |

| Spurious Free Dynamic Range (SFDR) <sup>2</sup>                     |                                                 | -75   |                                                     | dB                |                                                                                |

| Common Mode Rejection Ratio (CMRR) <sup>2</sup>                     |                                                 | <-70  |                                                     | dB                | For ripple frequency of 50/60Hz; see<br>Figure x.                              |

| Channel-to-Channel Isolation <sup>2</sup>                           |                                                 | -88   |                                                     | dB                |                                                                                |

| Bandwidth                                                           |                                                 | 100   | ļ                                                   | kHz               | @ -3 dB; PGA gain setting = 128                                                |

| DC ACCURACY                                                         |                                                 |       |                                                     |                   |                                                                                |

| Resolution                                                          |                                                 |       | 12                                                  | Bits              |                                                                                |

| Integral Nonlinearity <sup>2</sup>                                  |                                                 |       | ±1                                                  | LSB               |                                                                                |

| Differential Nonlinearity <sup>2</sup>                              |                                                 |       | ±0.99                                               | LSB               | Guaranteed no missed codes to 12 bits                                          |

| Offset Error <sup>2</sup>                                           |                                                 |       | ±5                                                  | LSB               | After Calibration                                                              |

| Offset Error Match <sup>2</sup>                                     |                                                 | ±1    |                                                     | LSB               |                                                                                |

| Offset Drift                                                        |                                                 | 5     |                                                     | μV/°C             |                                                                                |

| Gain Error <sup>2</sup>                                             |                                                 | ±0.1% | TBD                                                 | FSR               |                                                                                |

| Gain Error Match                                                    |                                                 | ±0.5  | 1                                                   | LSB               |                                                                                |

| ANALOG INPUT                                                        |                                                 |       |                                                     |                   |                                                                                |

| Input Voltage Range: V <sub>+</sub> and V <sub>-</sub> <sup>3</sup> | V <sub>CM</sub> -<br>V <sub>REF</sub> /(2xGain) |       | V <sub>CM</sub> +<br>V <sub>REF</sub> /(2xGai<br>n) | V                 | For Gain >1, $V_{CM} = AV_{CC}/2$                                              |

| Common mode Voltage, V <sub>CM</sub>                                | 2.5V- 100mV                                     |       | 2.5V<br>+100mV                                      | v                 | Common mode Voltage, $V_{CM}$                                                  |

| DC Leakage Current                                                  |                                                 |       | ±1                                                  | μΑ                |                                                                                |

| Input Capacitance                                                   |                                                 | 3     |                                                     | pF                |                                                                                |

| Input Impedance                                                     |                                                 | >1    | 1                                                   | GΩ                |                                                                                |

| REFERENCE INPUT/OUTPUT                                              |                                                 |       |                                                     |                   |                                                                                |

| Reference Output Voltage <sup>4</sup>                               | +2.49                                           |       | +2.51                                               | V                 | ±0.2% max @ 25°C                                                               |

| Reference Input Voltage Range                                       | +2.49                                           |       | +2.51                                               | v                 | _                                                                              |

| DC Leakage Current                                                  |                                                 |       | ±1                                                  | μΑ                | External reference applied to Pin<br>V <sub>REF</sub> A/Pin V <sub>REF</sub> B |

| Input Capacitance                                                   |                                                 | 25    |                                                     | pF                |                                                                                |

| V <sub>REF</sub> A, V <sub>REF</sub> B Output Impedance             |                                                 | 10    |                                                     | Ω                 |                                                                                |

| Reference Temperature Coefficient                                   |                                                 | 20    |                                                     | ppm/°C            |                                                                                |

| V <sub>REF</sub> Noise                                              |                                                 | 20    | -                                                   | μV <sub>RMS</sub> |                                                                                |

| LOGIC INPUTS                                                        | 1                                               |       |                                                     |                   |                                                                                |

| Input High Voltage, V <sub>INH</sub>                                | $0.7 \times V_{DRIVE}$                          |       |                                                     | V                 |                                                                                |

| Input Low Voltage, VINL                                             |                                                 |       | 0.8                                                 | V                 |                                                                                |

| Input Current, I <sub>IN</sub>                                      | 1                                               |       | ±1                                                  | μA                | $V_{IN} = 0 V \text{ or } V_{DRIVE}$                                           |

| Input Capacitance, C <sub>IN</sub> <sup>4</sup>                     |                                                 | 5     |                                                     | pF                |                                                                                |

|                                                                     |                                                 |       |                                                     |                   |                                                                                |

| LOGIC OUTPUTS                                                                                                                                                                                         |                      | !             |                                                      |                                                                |                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output High Voltage, Vон                                                                                                                                                                              | V <sub>DRIVE</sub> – |               |                                                      | v                                                              |                                                                                                                                                                                                   |

| output high voltage, von                                                                                                                                                                              | 0.2                  |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Output Low Voltage, V <sub>OL</sub>                                                                                                                                                                   |                      | -             | 0.4                                                  | V                                                              |                                                                                                                                                                                                   |

| Floating State Leakage Current                                                                                                                                                                        |                      |               | ±1                                                   | μA                                                             |                                                                                                                                                                                                   |

| Floating State Output Capacitance <sup>4</sup>                                                                                                                                                        |                      | 10            |                                                      | pF                                                             |                                                                                                                                                                                                   |

| Output Coding                                                                                                                                                                                         |                      | 1<br>1<br>1   |                                                      | Two's Con                                                      | nplement                                                                                                                                                                                          |

| CONVERSION RATE                                                                                                                                                                                       |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Conversion Time                                                                                                                                                                                       |                      | 1             | 560                                                  | ns                                                             | $18 \times t_{SCLK}$ , For $4.75V < V_{DRIVE} \le 5.25V$                                                                                                                                          |

| Cycle Time                                                                                                                                                                                            |                      |               | 969                                                  | ns                                                             | $31 \times t_{SCLK}$ , For 4.75V <v<sub>DRIVE <math>\leq</math> 5.25V</v<sub>                                                                                                                     |

| AC Acquisition Time <sup>4</sup>                                                                                                                                                                      |                      |               | 440                                                  | ns                                                             | For 4.75V <v<sub>DRIVE≤5.25V</v<sub>                                                                                                                                                              |

| Throughput Rate                                                                                                                                                                                       |                      |               | 1                                                    | MSPS                                                           | For 4.75V <v<sub>DRIVE≤5.25V</v<sub>                                                                                                                                                              |

|                                                                                                                                                                                                       |                      | >750          | TBD                                                  | KSPS                                                           | For 2.7V≤V <sub>DRIVE</sub> ≤4.75V                                                                                                                                                                |

| COMPARATORS                                                                                                                                                                                           |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Input Offset range                                                                                                                                                                                    |                      |               | ±4.5                                                 | mV                                                             |                                                                                                                                                                                                   |

| -                                                                                                                                                                                                     |                      | ±2.5          |                                                      | mV                                                             |                                                                                                                                                                                                   |

| Input Common Mode Range                                                                                                                                                                               |                      | 0 to 3.5      |                                                      | V                                                              |                                                                                                                                                                                                   |

| Input Impedance                                                                                                                                                                                       |                      | >1            |                                                      | GΩ                                                             |                                                                                                                                                                                                   |

| I <sub>DD</sub> Normal Mode (Static)                                                                                                                                                                  |                      |               |                                                      |                                                                | No Load, C <sub>OUT</sub> =0V                                                                                                                                                                     |

| Comparator A & B                                                                                                                                                                                      |                      | 0.90          |                                                      | μA                                                             | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                                                                                                         |

| <i>un</i>                                                                                                                                                                                             |                      | 1.80          |                                                      | μA                                                             | $C_{A}C_{B}V_{CC} = 5V$                                                                                                                                                                           |

| Comparator C & D                                                                                                                                                                                      |                      | 13            |                                                      | μA                                                             | $C_{C}C_{D}V_{CC} = 2.7V$                                                                                                                                                                         |

|                                                                                                                                                                                                       |                      | 27.0          |                                                      | μA                                                             | $C_{C}C_{D}V_{CC} = 5V$                                                                                                                                                                           |

| Propagation Delay Time- High to Low                                                                                                                                                                   |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Comparator A & B                                                                                                                                                                                      |                      | 2.30          |                                                      | μs                                                             | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                                                                                                         |

|                                                                                                                                                                                                       |                      | 1.70          |                                                      | μs                                                             | $C_{A}C_{B}V_{CC} = 5V$                                                                                                                                                                           |

| Comparator C & D                                                                                                                                                                                      |                      | 0.20          |                                                      | μs                                                             | $C_{C}C_{D}V_{CC} = 2.7V$                                                                                                                                                                         |

| <i>un</i>                                                                                                                                                                                             |                      | 0.14          |                                                      | μs                                                             | $C_{C}C_{D}V_{CC} = 5V$                                                                                                                                                                           |

| Propagation Delay Time- Low to High                                                                                                                                                                   |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Comparator A & B                                                                                                                                                                                      |                      | 1.70          |                                                      | μs                                                             | $C_{A}C_{B}V_{CC} = 2.7V$                                                                                                                                                                         |

|                                                                                                                                                                                                       |                      | 0.90          |                                                      | μs                                                             | $C_{A}C_{B}V_{CC} = 5V$                                                                                                                                                                           |

| Comparator C & D                                                                                                                                                                                      |                      | 0.210         |                                                      | μs                                                             |                                                                                                                                                                                                   |

|                                                                                                                                                                                                       |                      | 0.12          |                                                      | μs                                                             | $C_{C}C_{D}V_{CC} = 5V$                                                                                                                                                                           |

| POWER REQUIREMENTS                                                                                                                                                                                    |                      |               |                                                      |                                                                | Digital I/Ps = $0 V \text{ or } V_{DRIVE}$                                                                                                                                                        |

| AV <sub>DD</sub>                                                                                                                                                                                      | 4.75                 |               | 5.25                                                 | V                                                              | -                                                                                                                                                                                                 |

| DV <sub>DD</sub>                                                                                                                                                                                      | 4.75                 |               | 5.25                                                 | V                                                              | Throughput Rate = 1Msps                                                                                                                                                                           |

|                                                                                                                                                                                                       | 2.7                  |               | 4.75                                                 | V                                                              | Throughput Rate < 1Msps⁵                                                                                                                                                                          |

| $C_A C_B V_{CC}, C_C C_D V_{CC}$                                                                                                                                                                      | 2.7                  |               | 5.25                                                 | V                                                              |                                                                                                                                                                                                   |

|                                                                                                                                                                                                       | 2.7                  |               | 5.25                                                 | V                                                              |                                                                                                                                                                                                   |

|                                                                                                                                                                                                       |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Normal Mode (Static)                                                                                                                                                                                  |                      |               | 19                                                   | mA                                                             | $V_{DD} = 5.25 V$                                                                                                                                                                                 |

| Operational                                                                                                                                                                                           |                      |               | 24                                                   | mA                                                             | $f_s = 1$ MSPS, $V_{DD} = 5.25$ V                                                                                                                                                                 |

| Shut-Down Mode                                                                                                                                                                                        |                      |               | 1                                                    |                                                                |                                                                                                                                                                                                   |

|                                                                                                                                                                                                       |                      |               |                                                      |                                                                |                                                                                                                                                                                                   |

| Normal Mode (Operational)                                                                                                                                                                             |                      |               | 120                                                  | mW                                                             |                                                                                                                                                                                                   |

| Shut-Down                                                                                                                                                                                             |                      |               | 5.25                                                 | μW                                                             |                                                                                                                                                                                                   |

| "" Comparator C & D "" POWER REQUIREMENTS AV <sub>DD</sub> DV <sub>DD</sub> CA_CBVcc, Cc_CbVcc VDRIVE IDD Normal Mode (Static) Operational Shut-Down Mode Power Dissipation Normal Mode (Operational) | 4.75<br>2.7<br>2.7   | 0.90<br>0.210 | 5.25<br>4.75<br>5.25<br>5.25<br>19<br>24<br>1<br>120 | μs<br>μs<br>μs<br>V<br>V<br>V<br>V<br>V<br>V<br>mA<br>mA<br>μA | $C_{A}C_{B}V_{CC} = 5V$ $C_{C}C_{D}V_{CC} = 2.7V$ $C_{C}C_{D}V_{CC} = 5V$ Digital I/Ps = 0 V or V <sub>DRIVE</sub> Throughput Rate = 1Msps Throughput Rate < 1Msps <sup>5</sup> $V_{DD} = 5.25 V$ |

<sup>1</sup> Temperature range is -40°C to +105°C

<sup>2</sup> See Terminology section.

<sup>3</sup> For Gain =1 the maximum analog input signal is V<sub>CM</sub>±1.0V

<sup>4</sup> Refers to pins V<sub>REF</sub>A or V<sub>REF</sub>B.

<sup>5</sup> The AD7262 is functional but the performance specified in this specification table does not applies with these conditions.

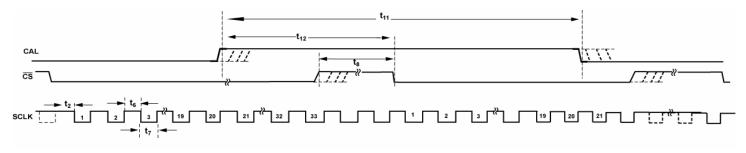

### TIMING SPECIFICATIONS

$AV_{CC} = DV_{CC} = 5 V \pm 5\%$ ,  $C_A\_C_BV_{CC} = C_C\_C_DV_{CC} = 2.7 V$  to 5.25V,  $V_{REF} = 2.5 V$  Internal/External;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Tał  | ole      | 4. |

|------|----------|----|

| T at | <i>n</i> | т. |

| Parameter                | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                                  | Unit    | Description                                                                      |

|--------------------------|----------------------------------------------|----------------------------------|---------|----------------------------------------------------------------------------------|

|                          | $2.7V \le V_{DRIVE} \le 4.75V$               | 4.75V <v<sub>DRIVE≤5.25V</v<sub> |         |                                                                                  |

| <b>f</b> <sub>SCLK</sub> | 100                                          | 100                              | kHz min |                                                                                  |

|                          | TBD                                          | 32                               | MHz max | For AD7262                                                                       |

|                          | TBD                                          | 34                               | MHz max | For AD7264                                                                       |

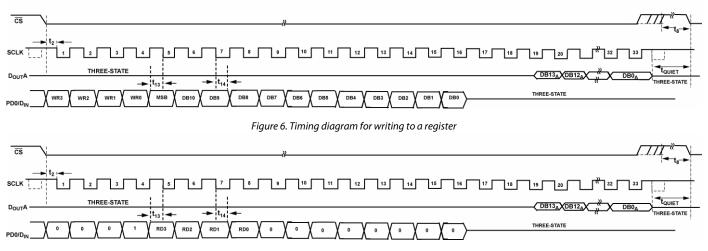

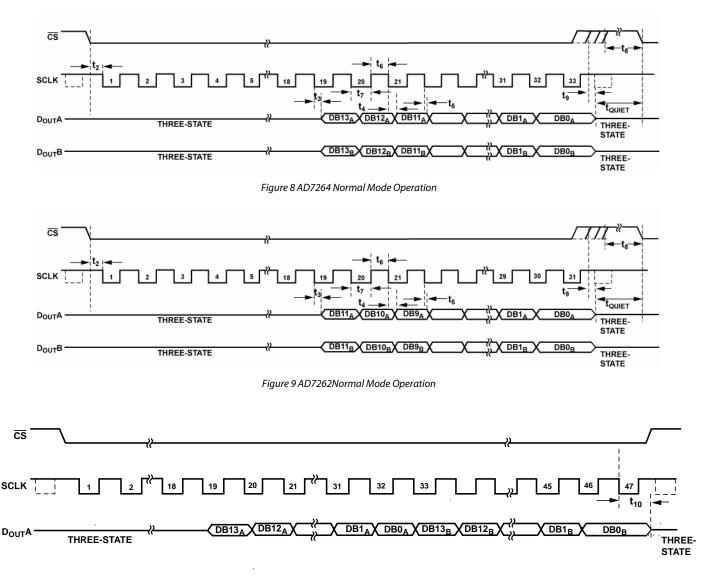

| <b>t</b> convert         | TBD                                          | $18 \times t_{SCLK}$             | ns max  | tSCLK = 1/fSCLK                                                                  |

|                          |                                              | 530                              | ns max  | For AD7264                                                                       |

|                          |                                              | 560                              | ns max  | For AD7262                                                                       |

| t <sub>Cycle</sub>       | $33 \times t_{SCLK}$                         | $33 \times t_{SCLK}$             | ns max  | $t_{SCLK} = 1/f_{SCLK}$ For AD7264                                               |

|                          |                                              | 970                              | ns max  | For AD7264                                                                       |

|                          | $31 \times t_{SCLK}$                         | $31 \times t_{SCLK}$             | ns max  | t <sub>SCLK</sub> = 1/f <sub>SCLK</sub> For AD7262                               |

|                          |                                              | 969                              | ns max  | For AD7262                                                                       |

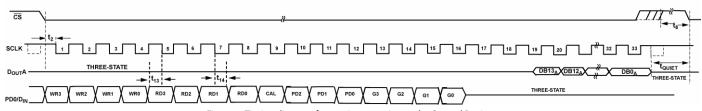

| <b>t</b> quiet           | 30                                           | 30                               | ns min  | Minimum time between end of serial read/Bus Relinquish and next                  |

|                          |                                              |                                  |         | falling edge of CS                                                               |

| t <sub>2</sub>           | 15                                           | 15                               | ns min  | $\overline{CS}$ to SCLK setup time,                                              |

| t <sub>3</sub>           | 15                                           | 15                               | ns max  | Delay from 19th SCLK falling edge until DOUTA and DOUTB are three-state disabled |

| t <sub>4</sub>           | TBD                                          | 25                               | ns max  | Data access time after SCLK falling edge,                                        |

| t <sub>5</sub>           | 5                                            | 5                                | ns min  | SCLK to data valid hold time,                                                    |

| t <sub>6</sub>           | 0.45 t <sub>SCLK</sub>                       | 0.45 t <sub>SCLK</sub>           | ns min  | SCLK high pulse width                                                            |

| t <sub>7</sub>           | 0.45 t <sub>SCLK</sub>                       | 0.45 t <sub>SCLK</sub>           | ns min  | SCLK low pulse width                                                             |

| t <sub>8</sub>           | 30                                           | 30                               | ns min  | CS rising edge to falling edge pulse width                                       |

| t <sub>9</sub>           | 15                                           | 15                               | ns max  | CS rising edge to DOUTA, DOUTB, high impedance / Bus Relinquish                  |

| <b>t</b> 10              | 5                                            | 5                                | ns min  | SCLK falling edge to DOUTA, DOUTB, high impedance                                |

|                          | 35                                           | 35                               | ns max  | SCLK falling edge to DOUTA, DOUTB, high impedance                                |

| <b>t</b> 11              | 2                                            | 2                                | µs min  | Minimum CAL pin high time                                                        |

| t <sub>12</sub>          | 2                                            | 2                                | µs min  | Minimum time between the CAL pin high and the $\overline{CS}$ falling edge.      |

| t <sub>13</sub>          | 4                                            | 4                                | ns min  | DIN set-up time prior to SCLK falling edge                                       |

| <b>t</b> <sub>14</sub>   | 2                                            | 2                                | ns min  | DIN hold time after SCLK falling edge                                            |

<sup>1</sup> Sample tested during initial release to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V. All timing specifications given are with a 25 pF load capacitance. With a load capacitance greater than this value, a digital buffer or latch must be used. See Terminology section and Figure TBD.

<sup>1</sup> The time required for the output to cross 0.4 V or 2.4 V.

### **Preliminary Technical Data**

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 5

| Parameter                                                                                       | Rating                                            |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------|

| V <sub>DRIVE</sub> to DGND                                                                      | -03V to DV <sub>CC</sub>                          |

| V <sub>DRIVE</sub> to AGND                                                                      | -03V to $AV_{CC}$                                 |

| AVcc to AGND, DGND                                                                              | -0.3V to +7V                                      |

| AV <sub>CC</sub> to DV <sub>CC</sub>                                                            | $DV_{CC}$ – 0.3V to 7V                            |

| DVcc to AVcc                                                                                    | -0.3V to AV <sub>CC</sub> +0.3V                   |

| DV <sub>CC</sub> to DGND                                                                        | -0.3V to +7V                                      |

| $C_A C_B V_{CC}$ to $C_A C_B GND$ ,                                                             | -0.3V to +7V                                      |

| $C_{C}C_{D}V_{CC}$ to $C_{C}C_{D}GND$ ,                                                         | -0.3V to +7V                                      |

| AGND to DGND                                                                                    | -0.3V to +0.3V                                    |

| $C_A C_B GND$ , $C_C C_D GND$ to                                                                | -0.3V to +0.3V                                    |

| DGND                                                                                            |                                                   |

| Analog Input Voltage to AGND                                                                    | -0.3V to AV <sub>CC</sub> +0.3V                   |

| Digital Input Voltage to DGND                                                                   | -0.3V to +7V                                      |

| Digital Output Voltage to GND                                                                   | -0.3V to $V_{DRIVE}$ +0.3V                        |

| $V_{REF}A$ , $V_{REF}B$ input to AGND                                                           | -0.3V to $AV_{CC}$ +0.3V                          |

| CoutA, CoutB, CoutC, CoutD to                                                                   |                                                   |

| GND                                                                                             | -0.3V to $V_{DRIVE}$ +0.3V                        |

| $C_A \pm$ , $C_B \pm$ , $C_C \pm$ , $C_D \pm$ , to<br>$C_A \_ C_B \_ GND$ , $C_C \_ C_D \_ GND$ | -0.3V to $C_A C_B V_{CC} / C_C C_D V_{CC} + 0.3V$ |

| Operating Temperature Range                                                                     | -40°C to +105°C                                   |

| Storage Temperature Range                                                                       | –65°C to +150°C                                   |

| Junction Temperature                                                                            | 150°C                                             |

| TQFP Package                                                                                    |                                                   |

| $\theta_{JA}$ Thermal Impedance                                                                 | TBD°C/W                                           |

| $\theta_{\rm JC}$ Thermal Impedance                                                             | TBD°C/W                                           |

| LFCSP Package                                                                                   |                                                   |

| $\theta_{JA}$ Thermal Impedance                                                                 | 25.88°C/W                                         |

| $\theta_{\rm JC}$ Thermal Impedance                                                             | TBD°C/W                                           |

| Pb-free Temperature, Soldering                                                                  |                                                   |

| Reflow                                                                                          | 255°C                                             |

| ESD                                                                                             | TBD kV                                            |

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

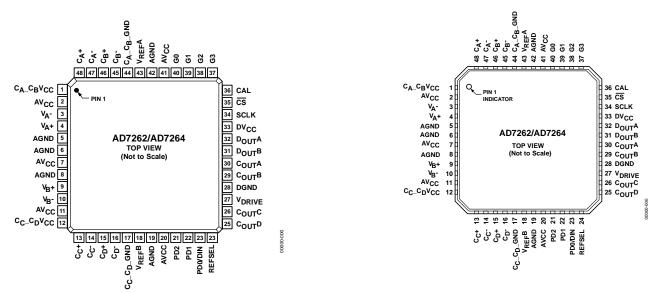

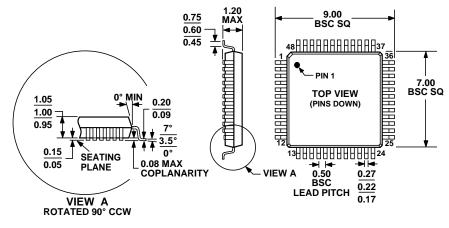

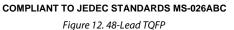

Figure 3: Pin Configuration for LFSCP Package (CP-4)

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2: Pin Configuration for TQFP Packager (SU-48)

Table 6. Pin Function Descriptions

| Pin No.              | Mnemonic                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |